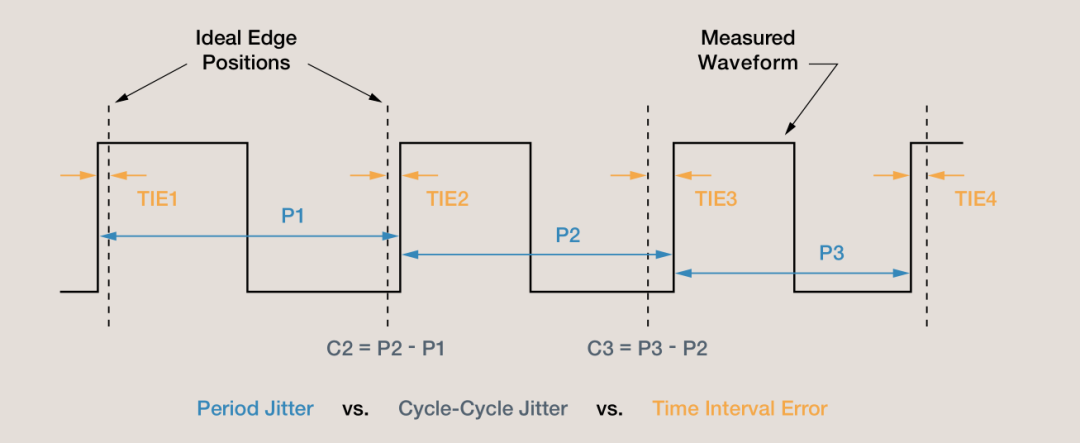

“抖动可以定义为数字信号在有效时点上偏离理想时间位置的短期变化。”周期信号的随机变化特性,在时域看是抖动,在频域看是相位噪声。抖动包括周期抖动、周期间抖动、时间间隔误差 (TIE)等。

随机性抖动是不能预测的定时噪声,因为它没有可以识别的模式。典型的随机性抖动实例是在无线电接收机调谐到没有活动的载频时听到的声音。尽管在理论上随机过程具有任意概率分布,但我们假设随机性抖动呈现高斯分布,以建立抖动模型。这种假设的原因之一是,在许多电路中,随机噪声的主要来源是热噪声 ( 也称为 Johnson 噪声或散粒噪声 ),而热噪声呈现高斯分布。另一个比较基础的原因是,根据中心极限定理,不管各个噪声源采用什么分布,许多不相关的噪声源的合成效应该接近高斯分布。

确定性抖动是可以复现、可以预测的定时抖动。正因如此,这个抖动的峰峰值具有上下限,在数量相对较少的观察基础上,通常可以以高置信度观察或预测其边界。

周期性抖动

由于任何周期波形都可以分解成傅立叶顺序的谐一般来说,周期性抖动与数据流中任何定期重复的模式无关。波相关正弦曲线,这类抖动有时称为正弦曲线抖动。周期性抖动一般是由耦合到系统中的外部确定噪声源引起的,如开关电源噪声或强局部 RF 载波。时钟恢复PLL 不稳定也可能会导致周期性抖动。

数据相关抖动

与数据流中的位序列相关的任何抖动都称为数据相关抖动或DDJ。DDJ通常是由电缆或设备的频响引起的。

占空比相关抖动

可以根据相关边沿是上升沿还是下降沿预测的抖动称为占空比抖动 (DCD),导致 DCD 的常见原因有两个:

1..上升沿的转换速率与下降沿的转换速率不同。

2..波形的判定阈值高于或低于应该值。

有界不相关抖动(BUJ)

高速互连的相邻通道之间的串扰,如 4.x.10GbE,明显影响着串行链路的性能。此外,存在串扰会损害传统电流抖动分离方法的精度,由于过量计算随机抖动,会导致高速链路器件的设计裕量下降。

子速率抖动(SRJ)

由于附近的逻辑处理,确定性抖动通常会感应到系统中。这类交互会导致抖动,抖动可能是同步的,也可能是异步的,属于 BUJ 类别 (“不相关”是指抖动与数据码型不相关 )。时钟同步抖动是这类抖动的典型特例。信号处理技术,如复用 / 解复用、通道编码、码组格式化和低速并行处理,都有可能会以时钟边界的整数倍位移边沿。

周期间抖动用来衡量信号在相邻周期之间的周期变化。TIE 抖动用来衡量相对于已知时钟或恢复时钟的定时误差。抖动会劣化系统性能,如果您没有时间捕捉抖动,那么抖动就会影响调试工作。现在,任何高速设计都必须处理抖动,许多串行数据标准也要求进行全面抖动测试。

许多串行总线中必须在没有硬件时钟的情况下进行TIE测量,可以使用软件恢复时钟时钟恢复技术有两种:一种方法是线性最小均方拟合,使用可用的数据构建时钟。时钟频率设成数据的平均频率,调节时钟的相位,以使 TIE达到最小;还有一种方法是锁相环(如标准PLL,俗称“黄金 PLL”,意思是高标准的),与上面的方法一样,使用标准 PLI构建时钟。

深圳总部:广东省深圳市南山区留仙大道南山

云谷创新产业园二期6栋一楼东座

深圳总部:广东省深圳市南山区留仙大道南山

云谷创新产业园二期6栋一楼东座

0755-8368 0722(8线)

0755-8368 0722(8线)

1403880343

1403880343

公众号

视频号

哔哩哔哩

抖音

粤公网安备 44030502008393号

粤公网安备 44030502008393号